存储器层次结构

本章的核心是:

- 一些常见的存储技术

- 存储器的层次结构

- 高速缓存的工作原理

- 结合高速缓存,提高程序的

局部性

存储技术

有哪些与时俱进的存储技术?

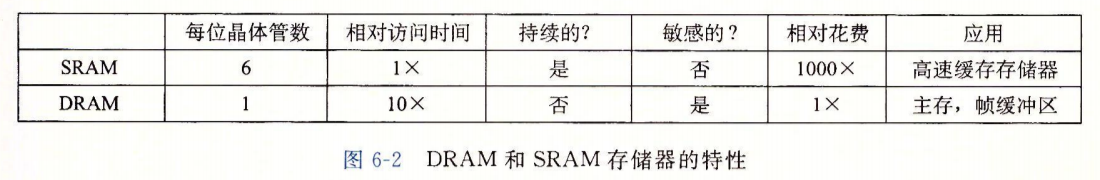

- SRAM:六晶体管电路,只要有电,就永远保持它的值。受干扰影响小。

DRAM:电容,易受干扰。

传统的DRAM

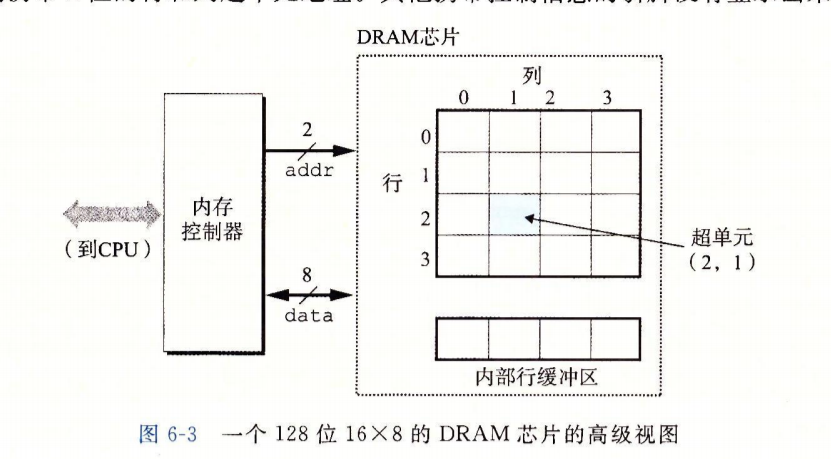

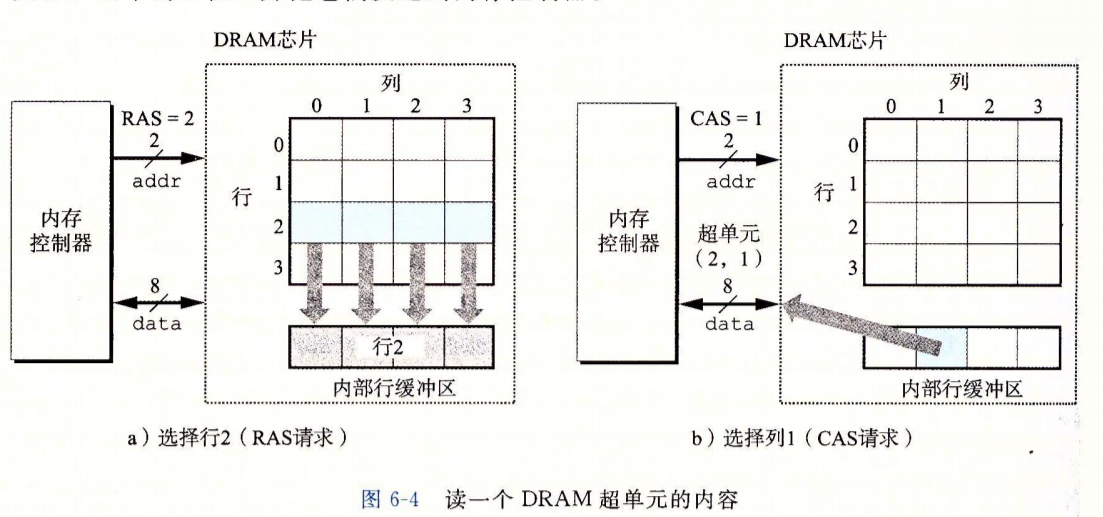

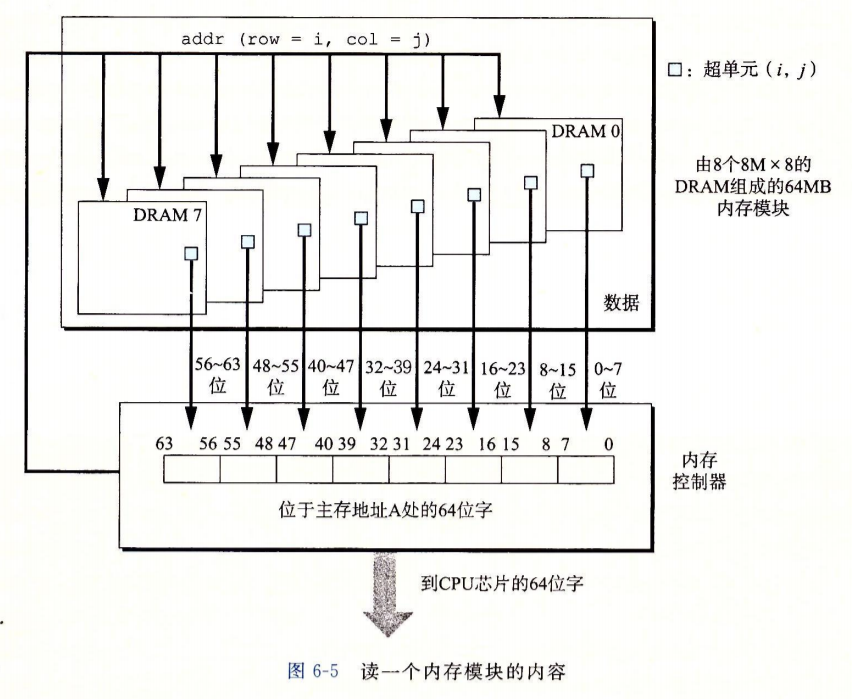

每个超单元都有w个DRAM单元

内存模块

增强的DRAM:对传统的DRAM进行优化,提高访问速度

- 非易失性存储器(历史原因,也叫ROM):断电依然保存信息

- PROM(可编程ROM):高电流熔断,只可编程一次

- EPROM(可擦可编程ROM):紫外光编程,可编程1000次

- EEPROM(电子可擦除ROM):无需要独立的特殊设备,可编程100000次

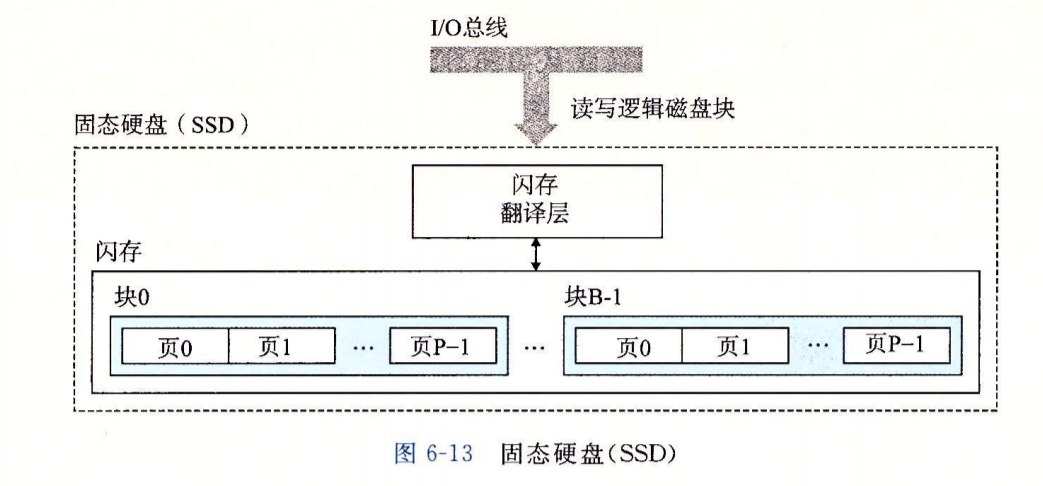

- 闪存:基于EEPROM

ROM有什么用?

存放在ROM中的程序被称为固件,比如PC的BIOS程序

当计算机通电以后,它会运行ROM中的固件

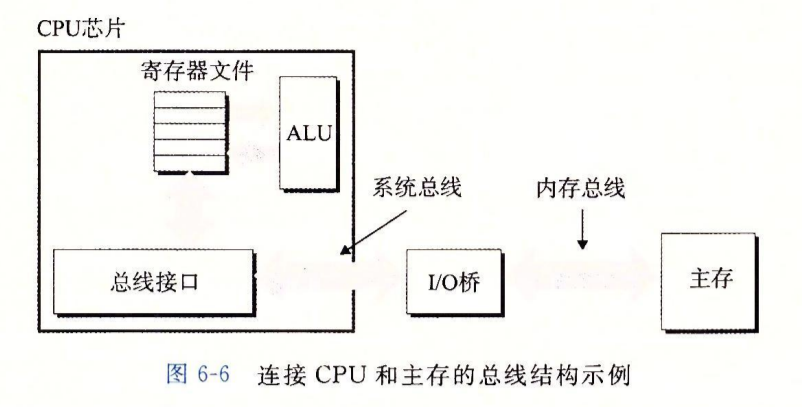

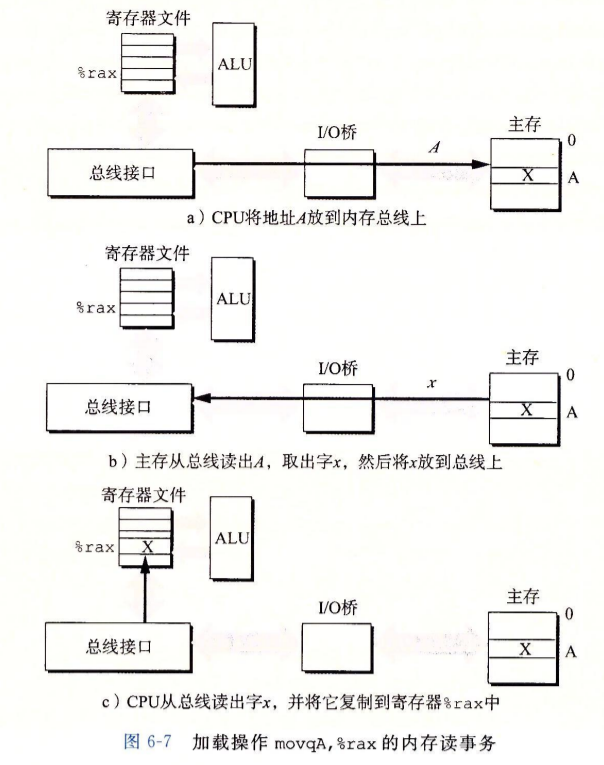

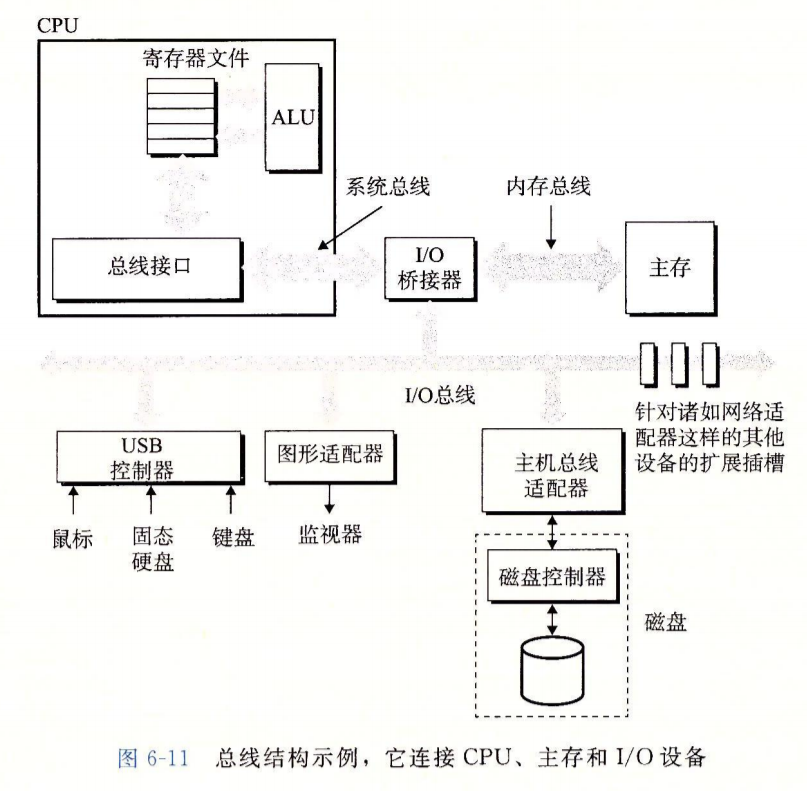

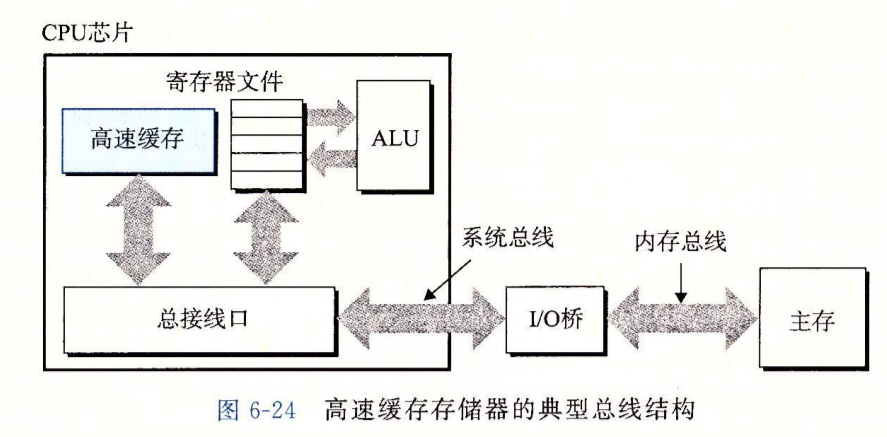

如何访问主存?

通过总线

I/O桥把系统总线的电子信号翻译成内存总线的电子信号

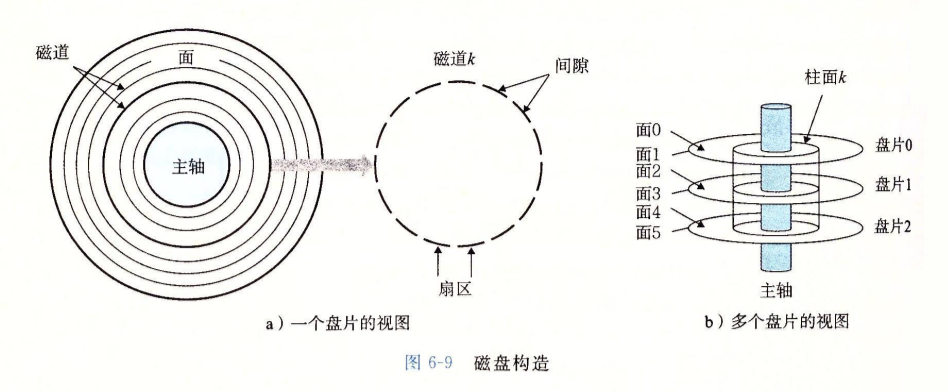

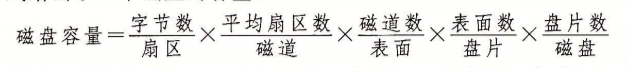

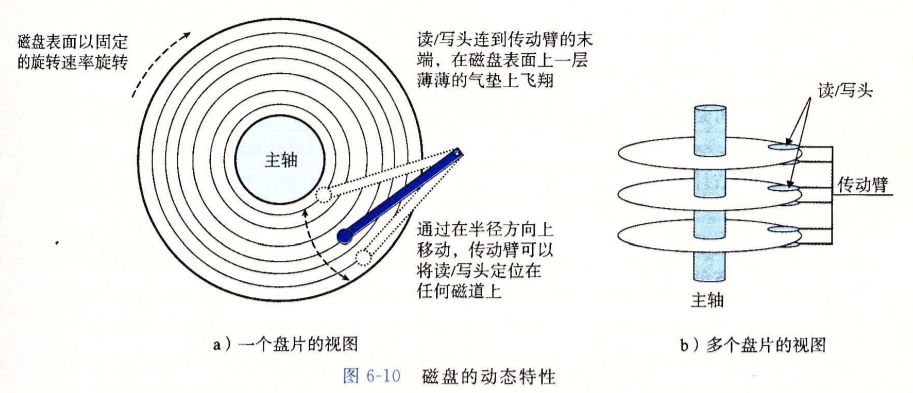

磁盘的构造?磁盘的容量?

使用磁性记录材料来记录信息

如何操作磁盘?如何连接磁盘?如何访问磁盘?

为了对操作系统隐藏这样的复杂性,根据扇区定义逻辑块

磁盘控制器维护逻辑块号和实际磁盘扇区之间的映射关系

通过I/O总线连接磁盘:

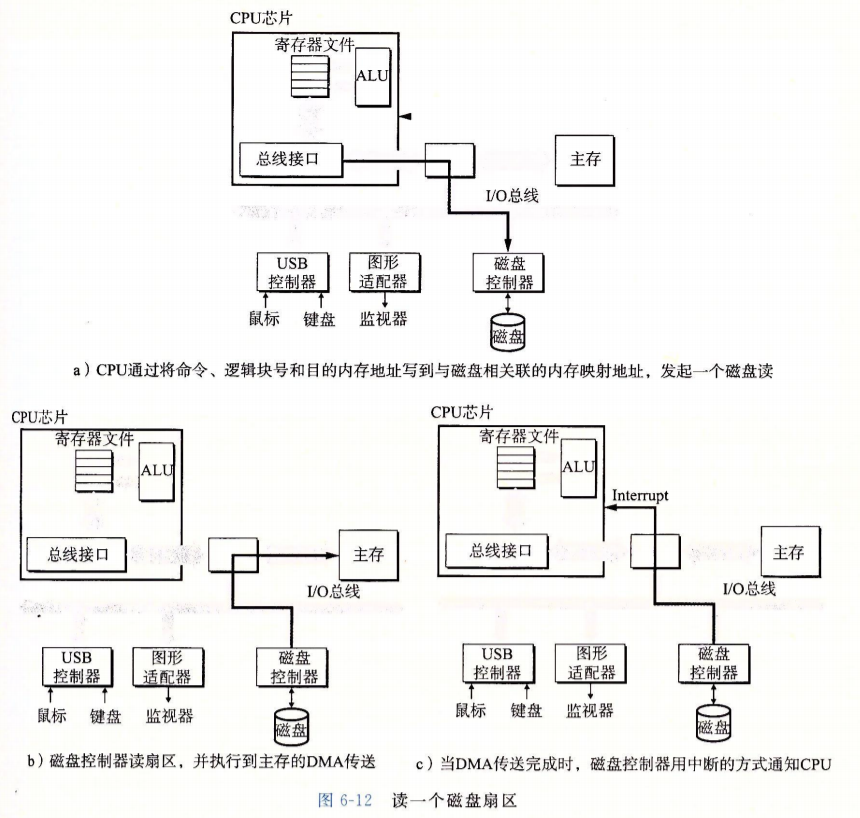

什么是直接内存访问(DMA)?

设备自己执行读和写总线事务,不需要CPU干涉,称为直接内存访问

固态硬盘的结构?

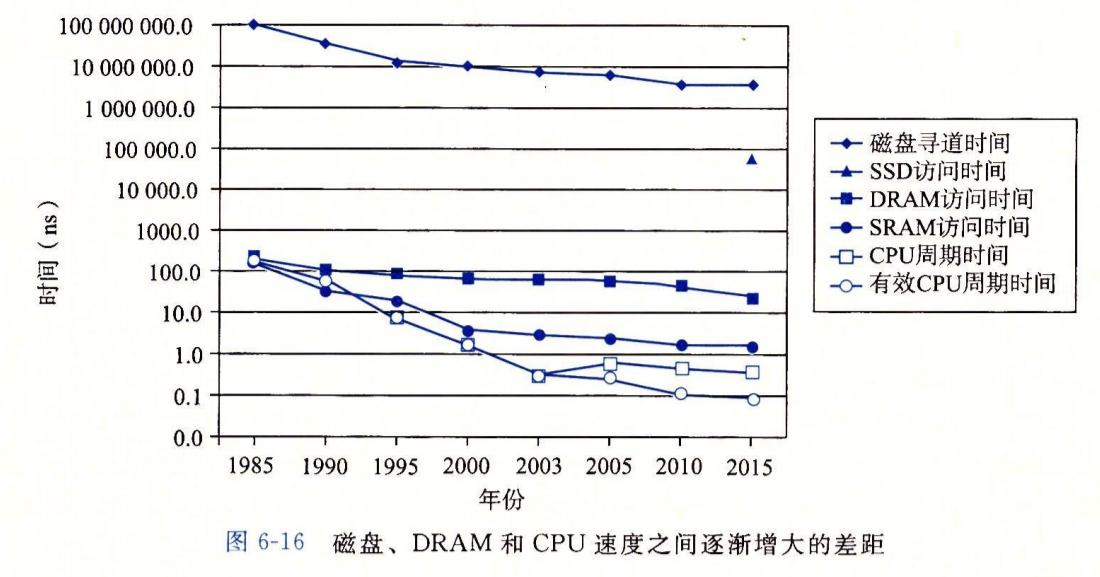

存储技术的趋势?

现代计算机频繁使用高速缓存来弥补处理器-内存之间的差距

程序的局部性能使高速缓存的作用发挥到极致

局部性

什么是局部性?

- 时间局部性:被引用过一次的内存地址,在不久之后多次被引用

- 空间局部性:被引用过一次的内存地址,在不久之后其附近的位置多次被引用

如何简单的运用局部性?

- 重复引用相同的变量具有良好的时间局部性

- 迭代数组的步长越小,空间局部性越好

- 循环体具有良好的时间和空间局部性

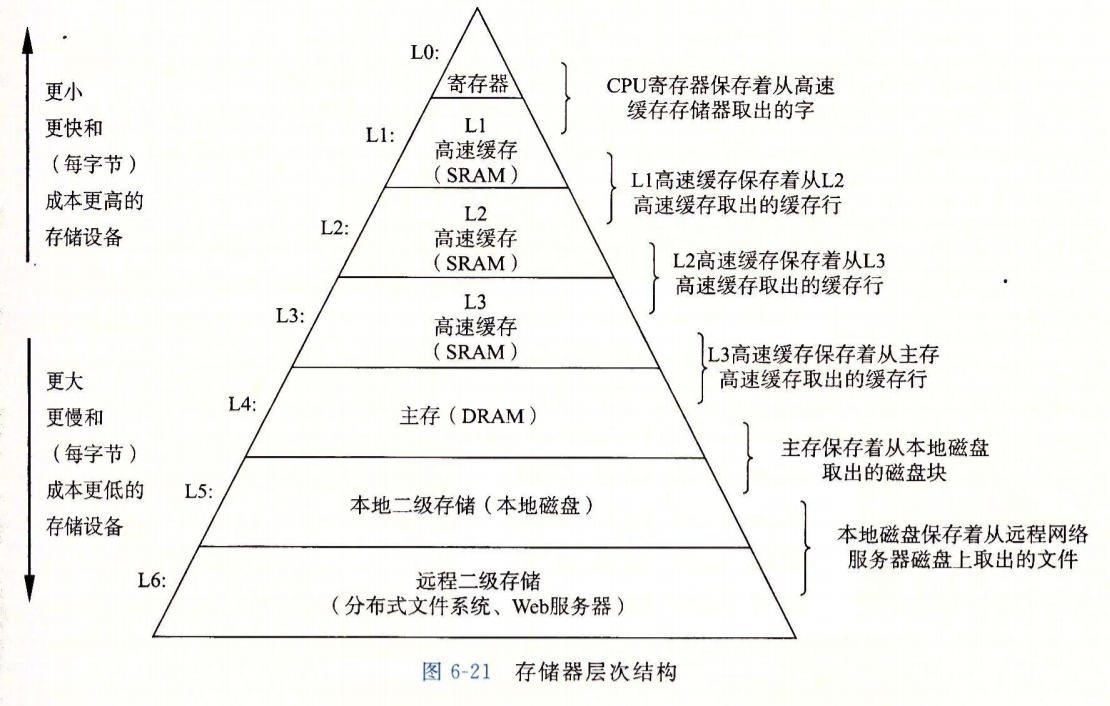

存储器层次结构

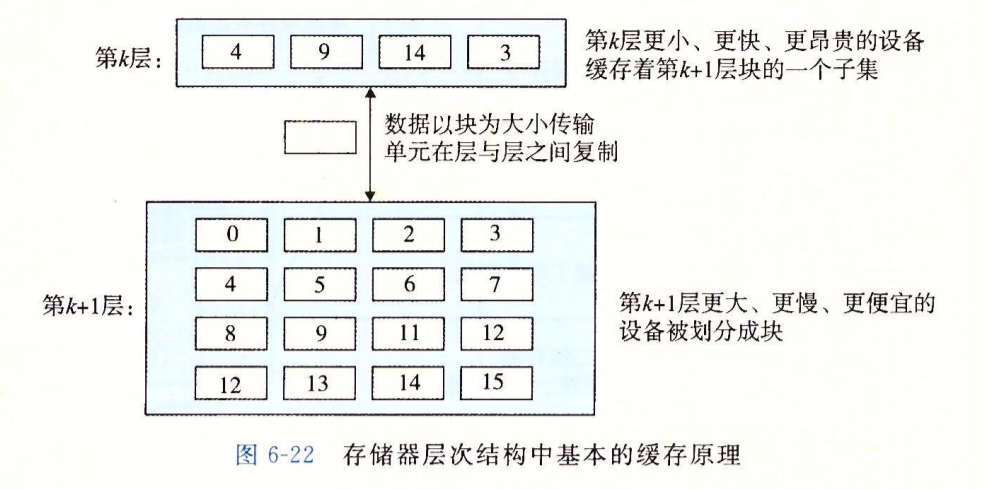

缓存的基本原理?

层与层之间以相同大小的数据块进行传输

不同层之间的块的大小是不一样的

缓存的命中和不命中?

找到了就是命中,没找到就是不命中

不命中的情况下需要决定替换块的替换策略

不命中的类型?

- 冷缓存:初始状态,什么缓存都没

- 冲突不命中:请求的缓存交替的发生在相同位置的块上

- 容量不命中:缓存太小了

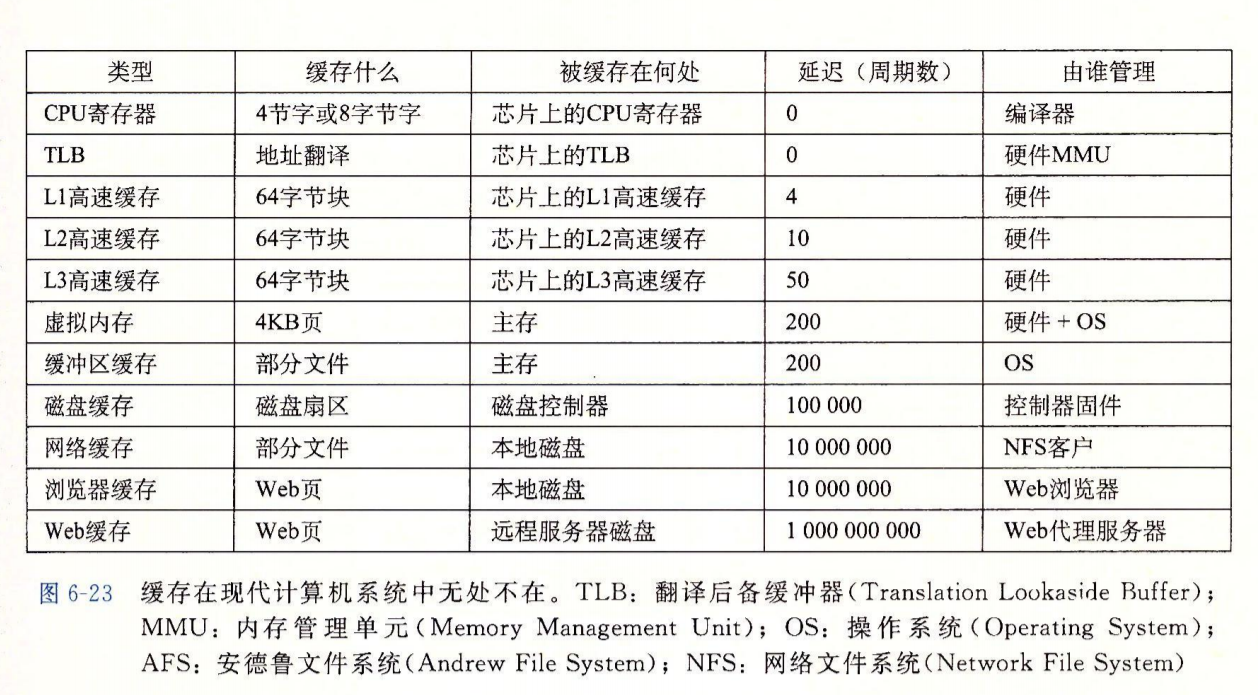

缓存的管理?

块的划分、块的传送、命中判定、替换策略等等

逐步从直接访问变为间接访问

高速缓存存储器

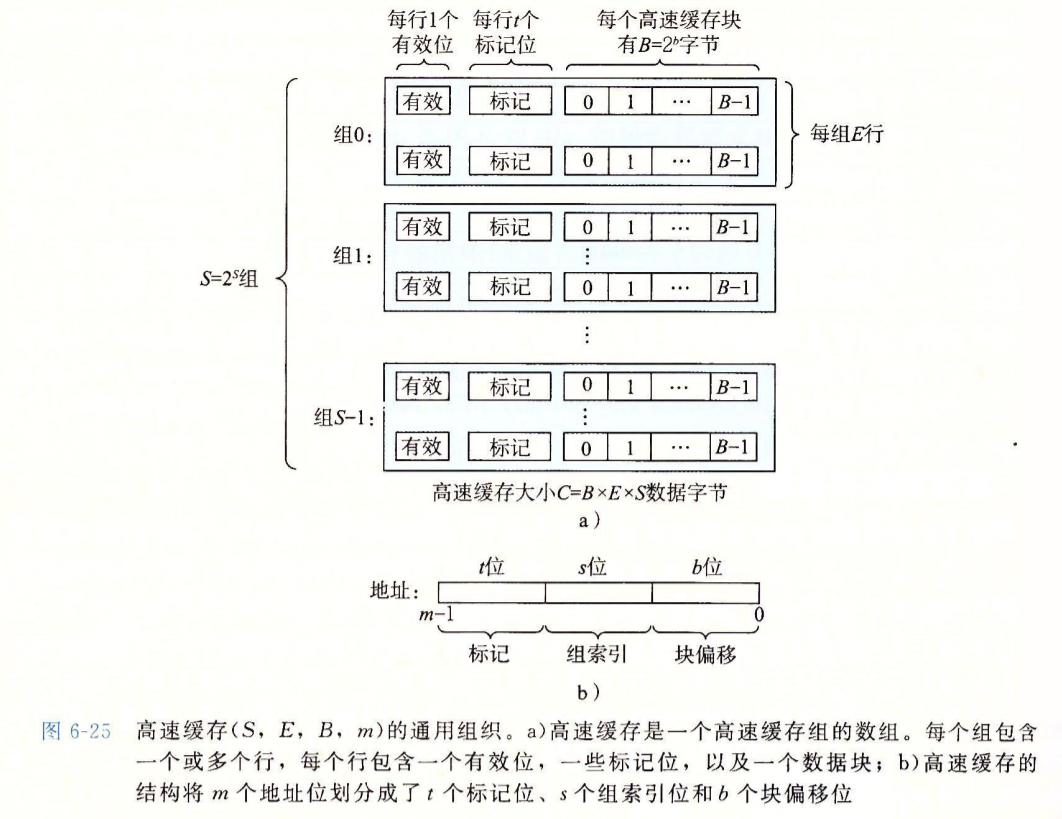

如何缓存(如何映射)?

缓存的位置都是根据地址计算得到

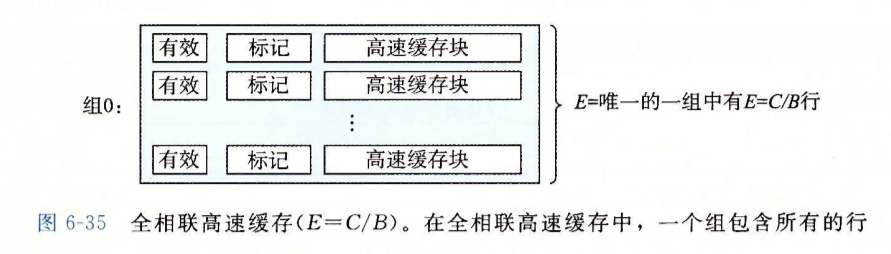

高速缓存的结构可以用元祖(S,E,B,m)描述

缓存类别有?

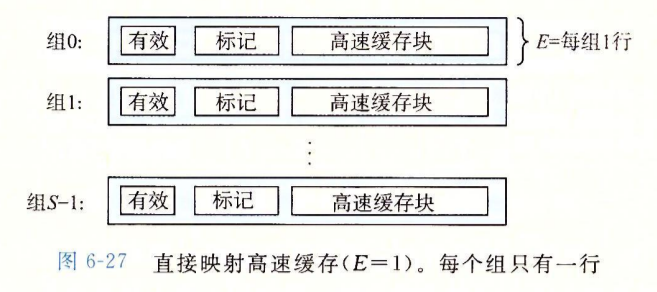

直接映射高速缓存

每组只有一行,替换策略简单,冲突不命中易发生

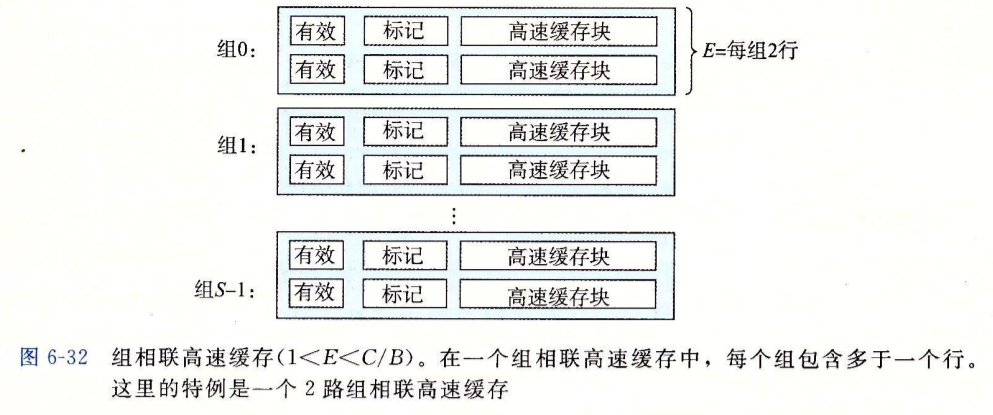

组相联高速缓存

每组有多行,最简单的替换策略是随机替换

全组高速缓存

命中如何更新缓存?

- 直写:立即向低层更新数据

- 写回:等待缓存被替换时才 向低层更新数据

不命中如何更新缓存?

- 写分配:先加载到高速缓存中

- 非写分配:直接更新,避开高速缓存

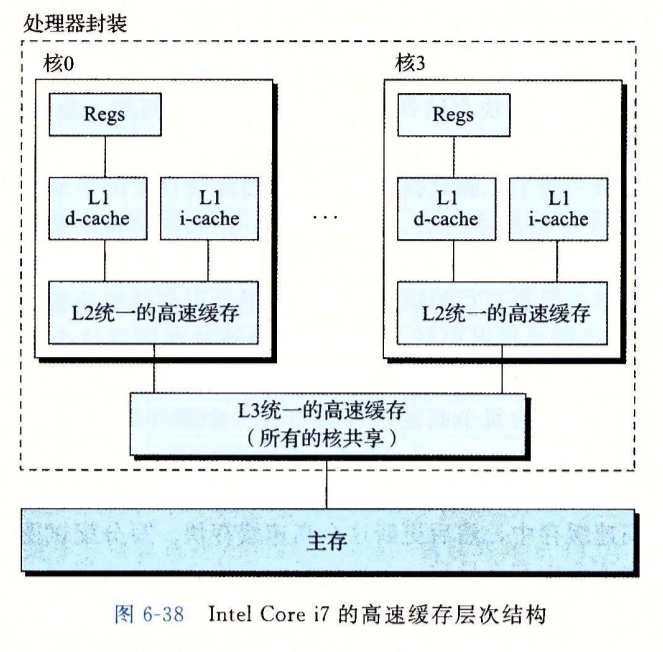

真实的缓存层次结构?

如何衡量缓存性能?

- 不命中率:不命中数量/引用数量

- 命中率:

- 命中时间:命中需要的时间

- 不命中处罚:不命中需要的额外时间

编写高速缓存友好的代码

确保代码高速缓存友好的方式是?

- 把时间花在核心函数中

- 尽量减少每个循环内部的缓存不命中率

空间局部性和缓存大小有直接关系

对存储器山如何分析?